Instructions and data stored in the same place Relies of both Combinational Logic and Sequential Logic Controlled by Finite State Machine

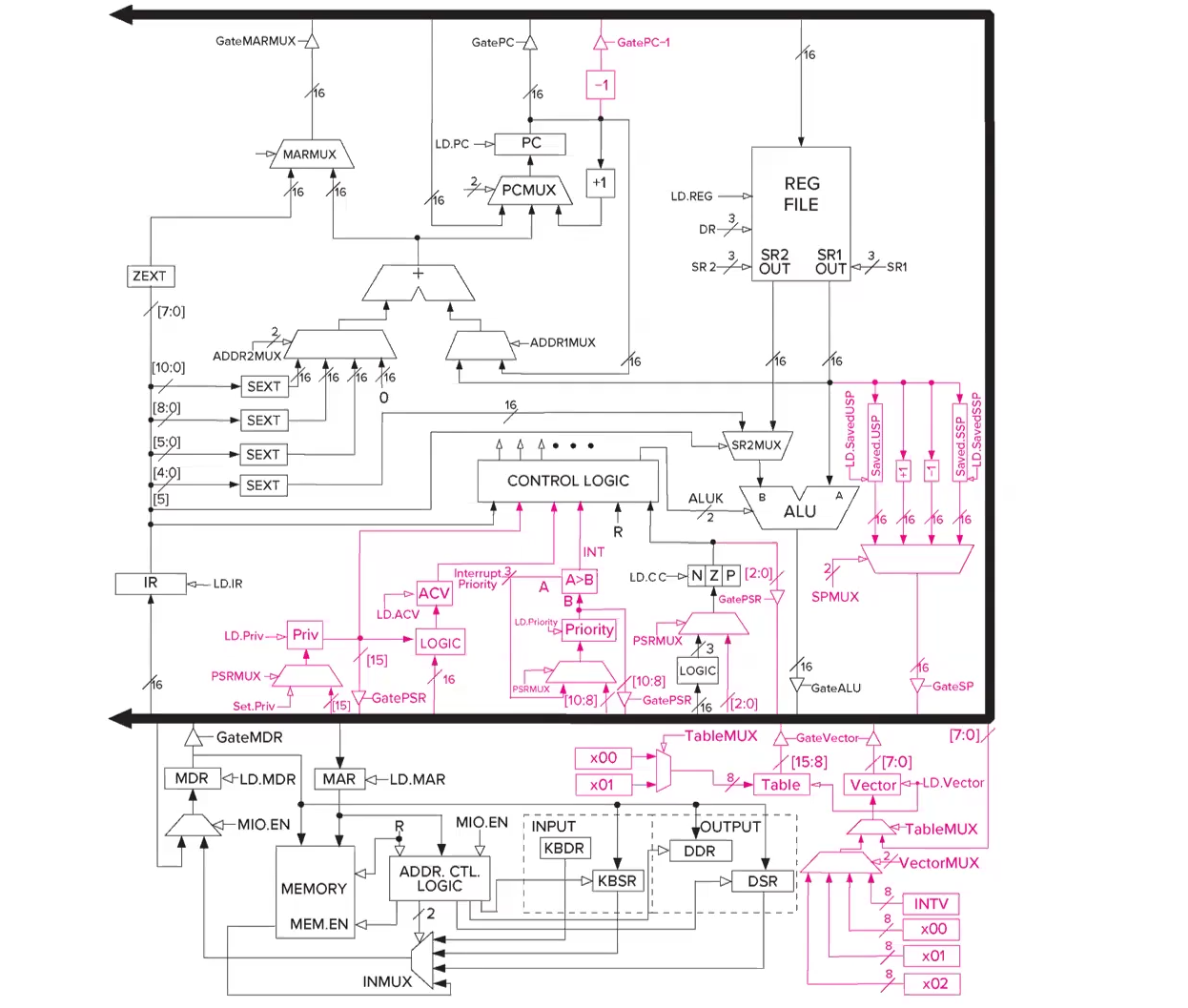

Datapath

Full Datapath

Simplified Datapath

Components

- 8 registers in the Register File

- ALU

- ROM

- RAM

- Finite State Machine

- Program Counter

Instructions

ALU Instructions

ADD

AND

Load Instructions

LD

LDR

LDI

LEA

Store Instructions

Control Instructions

BR

JMP

JSR

RET

RTI

TRAP

3 Macrostates of LC3

Fetch

3 Clock Cycles Gets the next instruction from Memory and puts it in the Instruction Register

Decode

Is like a dictionary for how to do an Instruction The Opcode actually goes into a Decoder, which chooses the relevant instruction to be performed.