RISC

[[Architecture#Style#Register-Register]]

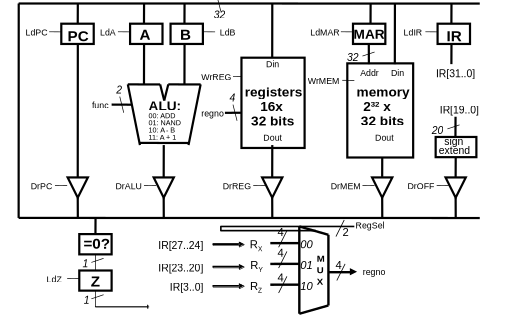

Fixed length, 32 bit, MIPS-like instructions

32 bit words, word addressable

16 registers

Not Dynamically Relocatable

RISC

[[Architecture#Style#Register-Register]]

Fixed length, 32 bit, MIPS-like instructions

32 bit words, word addressable

16 registers

Not Dynamically Relocatable

Register Convention

See LC2200 Calling Convention as well

| Reg # | Name | Use | Saved? |

|---|---|---|---|

| 0 | $zero | always zero (by hardware) | |

| 1 | $at | reserved for assembler | |

| 2 | $v0 | return value | no |

| 3-5 | $a0-$a2 | function args | no |

| 6-8 | $t0-$t2 | temporaries | Caller - if needed |

| 9-11 | $s0-$s2 | saved registers | Callee - if needed |

| 12 | $k0 | OS/traps only | |

| 13 | $sp | stack pointer | no |

| 14 | $fp | frame pointer | Callee - always |

| 15 | $ra | return address | no |

Instruction Set

See Instruction Set Architecture

Instructions

add

nand

addi

lw

lea

sw

beq

bgt

blt

jalr

halt

Types

R Type

opcode | reg 1 | reg 2 | unused filler | reg3 add, nand Register Addressing Mode

I Type

opcode | reg 1 | reg 2 | immediate addi, lw, sw, beq, lea, bgt, blt PC-Relative, Base + Offset, Immediate Addressing Mode

J Type

opcode | reg 1 | reg 2 | unused filler jalr Register Addressing Mode

O Type

opcode | unused halt No Addressing Mode